The SONOS cell uses a distributed charge trap design relying on a Silicon-Oxide-Nitride-Oxide-Silicon layout, and the company points to an effective silicon nitride film in the middle where the charges are trapped to allow for high retention. The company says that a standard modern memory cell with this level of control would only be able to retail the data for around 100 seconds, and so the secret in the design is to do with a new type of flash cell they have developed. Still in the prototype stage, this 7bpc flash chip, likely in a WORM scenario, has an effective 10-year retention time for the data at 150C.

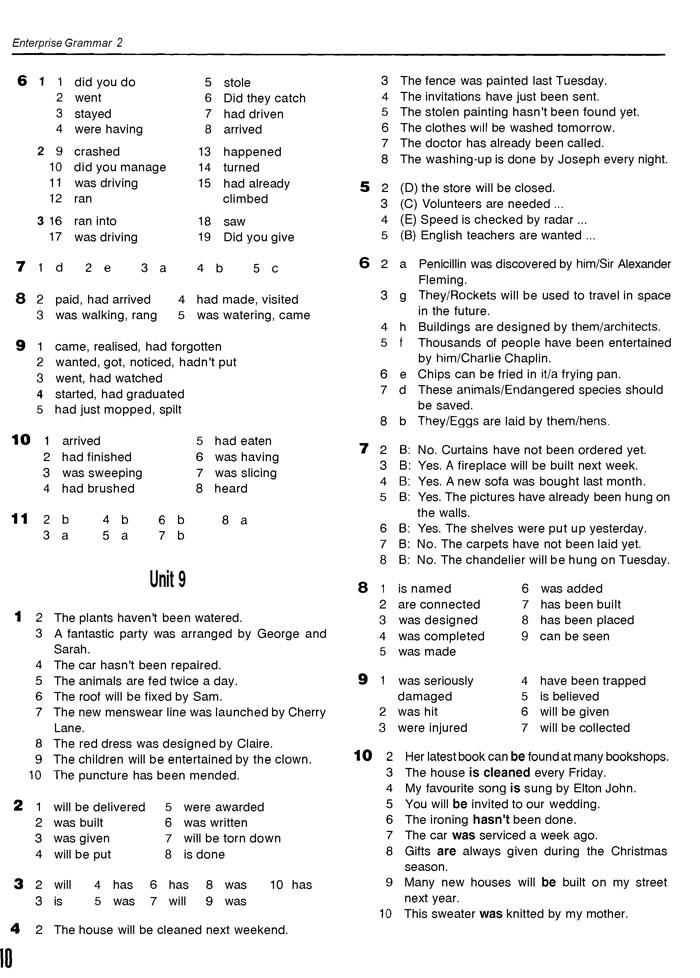

Enterprise 2 grammar series#

Some of the major vendors have been working on 5bpc storage, although the low endurance may make the technology only good for WORM – write once, read many, which is a common acronym for the equivalent of something like an old-school CD or non-rewritable DVD.įloadia Corp., a Series C startup from Japan, issued a press release this week to state that it has developed storage technology capable of seven bits-per-cell (7bpc). Right now the market seems happy with three bits-per-cell (3bpc) for performance and four bits-per-cell (4bpc) for capacity, with a few 2bpc designs for longer term endurance.

Image courtesy of Plextor, up to 4 bits-per-cell A Japanese company is now ready to start talking about their new 7 bits-per-cell solution. We’ve seen commercialization of storage up to four bits-per-cell, and talk about five. The easy jump of one to two bits-per-cell gives a straight 100% increase, in exchange for more control needed to read/write the bit but also limits the cell endurance.

Enterprise 2 grammar drivers#

One of the key drivers to increase capacity in next generation storage has been to increase the number of bits that can be stored per cell.

0 kommentar(er)

0 kommentar(er)